### IUT - Département Informatique

M3.101

## **SYSTEME**

## Principes des Systèmes d'Exploitation

Michel Billaud michel.billaud@u-bordeaux.fr Département Informatique - IUT - Université de Bordeaux Novembre 2014

Ce document est copiable et distribuable librement et gratuitement à la condition expresse que son contenu ne soit modifié en aucune façon, et en particulier que le nom de son auteur et de son institution d'origine continuent à y figurer.

## Table des matières

| 1 | Ordi | inateurs et systèmes                                                             |

|---|------|----------------------------------------------------------------------------------|

|   | 1.1  | Le premier ordinateur                                                            |

|   |      | 1.1.1 Les calculateurs électroniques                                             |

|   |      | 1.1.2 Mémoire à tube de Williams-Kilburn                                         |

|   |      | 1.1.3 Architecture et programmation                                              |

|   |      | 1.1.4 Une démontration probante                                                  |

|   |      | 1.1.5 Les suites                                                                 |

|   | 1.2  | Structure d'un ordinateur simple                                                 |

|   |      | 1.2.1 La mémoire                                                                 |

|   |      | 1.2.2 Le processeur                                                              |

|   |      | 1.2.3 Les périphériques                                                          |

|   |      | 1.2.4 Les outils de programmation                                                |

|   | 1.3  | Utilisation en mono-tâche                                                        |

|   |      | 1.3.1 Moniteur d'enchaînement des travaux                                        |

|   |      | 1.3.2 Planification de travaux                                                   |

|   |      | 1.3.3 Modifications matérielles nécessaires                                      |

|   |      | 1.3.4 Déroulement d'un appel système                                             |

|   | 1.4  | Profiter des temps morts : la multiprogrammation                                 |

|   |      | 1.4.1 Motivation économique                                                      |

|   |      | 1.4.2 Étude d'un cas                                                             |

|   |      | 1.4.3 La mise en oeuvre du multitâche                                            |

|   | 1.5  | Fonctionnement d'un centre de calcul                                             |

|   | 1.6  | Travailler à plusieurs : le temps partagé                                        |

|   | 1.7  | De nos jours                                                                     |

| _ | _    |                                                                                  |

|   |      | processus 1                                                                      |

|   |      | Introduction                                                                     |

|   | 2.2  |                                                                                  |

|   |      | 2.2.1 Multitâche       1         2.2.2 Exemple : intérêt du multi-tâches       1 |

|   |      | 2.2.3 Du batch au time sharing                                                   |

|   |      | 2.2.4 Support matériel du multi-tâches : les interruptions                       |

|   |      | 2.2.4 Support logiciel                                                           |

|   | 23   | Définitions 1                                                                    |

|   |      | 2.3.1 Les processus                                                              |

|   |      | 2.3.2 Les états des processus                                                    |

|   |      | 2.3.3 Changements d'état                                                         |

|   |      | 2.3.4 Multitâche coopératif                                                      |

|   |      | 2.3.5 Scénario détaillé                                                          |

|   |      | 2.3.6 Multitâche préemptif                                                       |

|   |      | 2.3.7 Multitâche préemptif et utilisation interactive                            |

|   |      | 2.3.8 Interruptions et multitâche, en résumé                                     |

|   | 2.4  | Politiques d'ordonnancement                                                      |

|   |      | 2.4.1 Ordonnanceur                                                               |

|   |      | 2.4.2 Critères d'évaluation                                                      |

|   |      | 2.4.3 Tourniquet                                                                 |

|   |      | 2.4.4 Priorités                                                                  |

|   |      | 2.4.5 Priorités variables                                                        |

|   |      | 2.4.6 Files multiples                                                            |

| 3 | Gest | ion de la Mémoire                                                                |

|   |      | Mémoire et multi-programmation                                                   |

|   |      | 3.1.1 Motivation                                                                 |

|   |      | 3.1.2 Rappel : fonctionnement de la mémoire                                      |

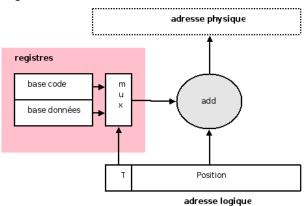

|   | 3.2  | Adresses logiques et physiques                                                   |

|   |      | 3.2.1 Le chargement des processus en mémoire                                     |

|   |      | 3.2.2 Adresses logiques                                                          |

|   |      | 3.2.3 Protection mémoire                                                         |

|   |      | 3.2.4 Memory Management Unit                                                     |

|   | 3.3  | Gestion d'un espace mémoire linéaire                                             |

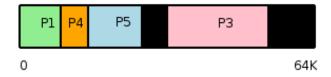

|   |      | 3.3.1 Exemple                                                                    |

|   |      | 3.3.2 Problème : la fragmentation                                                |

|   |      | 3.3.3 Solutions curatives                                                        |

|   |      | 3.3.4 Solutions préventives                                                      |

|   |      | 3.3.5 Buddy system (blocs compagnons)                                            |

|   | ٠.   | 3.3.6 Partitions de taille fixe                                                  |

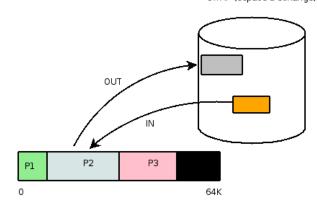

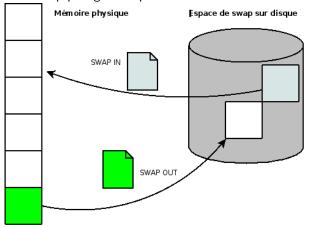

|   |      | Va-et-vient sur disque                                                           |

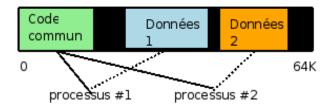

|   | 3.5  | La mémoire segmentée                                                             |

|   |      | 3.5.1 Segments                                                                   |

|   |      | 3.5.3 La réalisation                                      |    |

|---|------|-----------------------------------------------------------|----|

|   |      | 3.5.4 Tables locale/globale des segments                  | 30 |

|   |      | 3.5.5 Espace mémoire paginé                               | 31 |

|   |      | 3.5.6 Un circuit MMU : le MC68851                         | 32 |

|   | 3.6  | Mémoire virtuelle paginée                                 | 32 |

|   |      | 3.6.1 Principe                                            | 32 |

|   |      | 3.6.2 MMU pour la mémoire virtuelle paginée               | 33 |

|   |      | 3.6.3 Les algorithmes de remplacement de page             |    |

|   |      | 3.6.4 Remplacement à tour de rôle                         | 33 |

|   |      | 3.6.5 Algorithme LRU : least recently used                | 34 |

|   |      | 3.6.6 NRU, remplacement d'une page non récemment utilisée |    |

|   |      | 3.6.7 Algorithme de la seconde chance                     |    |

|   |      | 3.6.8 Algorithme du vieillissement                        | 32 |

|   |      | 3.6.9 Réservation d'espace d'échange                      |    |

|   |      | 3.6.10 Intérêt du swap?                                   |    |

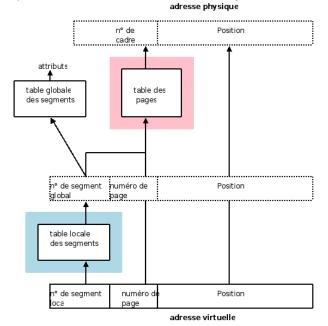

|   | 2 7  | Mémoire virtuelle segmentée-paginée                       |    |

|   | 3.1  | Memoire Virtuelle segmentee-paginee                       | 30 |

| 4 | Cost | ion des fichiers                                          | 38 |

| • |      | Les fichiers                                              |    |

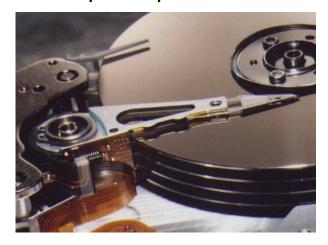

|   |      | Les disaues                                               |    |

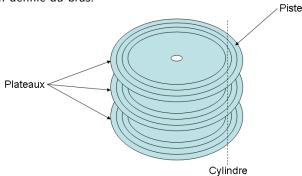

|   | 4.2  | Les disques :                                             |    |

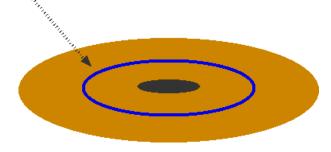

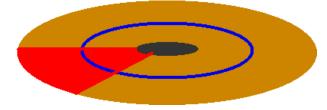

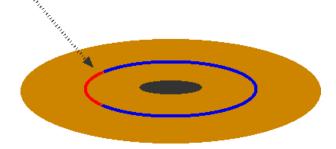

|   |      | 4.2.1 Disque, tete 4.2.2 Avec plusieurs plateaux          |    |

|   |      | 4.2.3 Quelques chiffres                                   |    |

|   | 4.2  | Gestion des entrées/sorties sur disque                    |    |

|   | 4.3  |                                                           |    |

|   |      | 4.3.1 Sur un système mono-tâche                           |    |

|   |      | 4.3.2 Sur un système multitâche                           |    |

|   |      | 4.3.3 E/S: Premier arrivé, premier servi                  |    |

|   |      | 4.3.4 E/S: plus court déplacement                         |    |

|   |      | 4.3.5 Politique de l'ascenseur                            | 41 |

|   |      | 4.3.6 E/S : Deadline driven disk scheduler                | 41 |

|   |      | 4.3.7 Conclusion                                          |    |

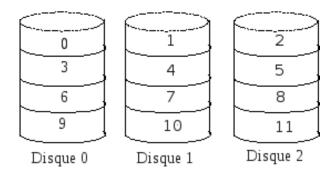

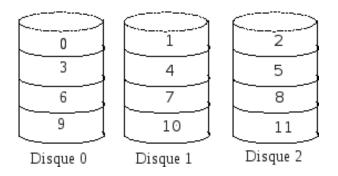

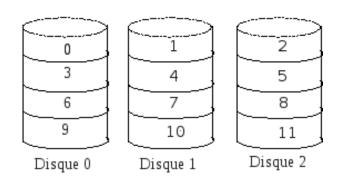

|   | 4.4  | Systèmes RAID                                             |    |

|   |      | 4.4.1 Principe et objectifs                               |    |

|   |      | 4.4.2 NRAID (JBOD)                                        |    |

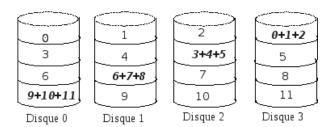

|   |      | 4.4.3 RAID 0 : agrégation par bandes                      |    |

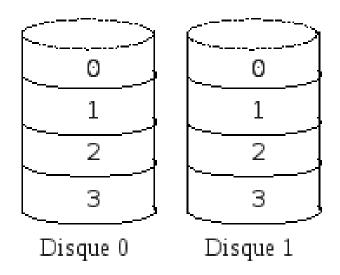

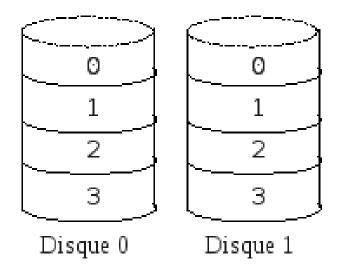

|   |      | 4.4.4 RAID 1: miroir                                      |    |

|   |      | 4.4.5 Disques de rechange, reconstruction                 |    |

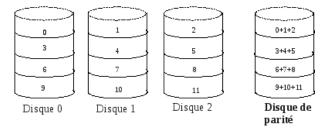

|   |      | 4.4.6 RAID 4 : agrégation par bandes avec parité          |    |

|   |      | 4.4.7 RAID 5 : agrégation par bandes avec parité répartie | 44 |

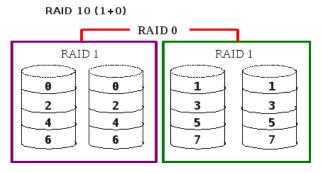

|   |      | 4.4.8 Combinaisons : RAID 10                              | 44 |

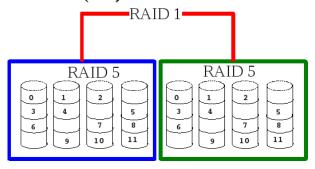

|   |      | 4.4.9 RAID 51                                             | 45 |

|   |      | 4.4.10 RAID 50                                            | 45 |

|   |      | 4.4.11 Choix d'un système RAID                            | 45 |

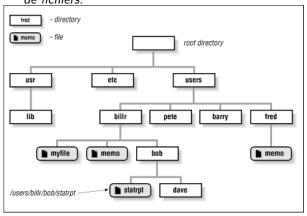

|   | 4.5  | Systèmes de fichiers                                      |    |

|   |      | 4.5.1 Fonctions du SGF                                    |    |

|   |      | 4.5.2 Catalogue de fichiers                               |    |

|   |      | 4.5.3 FAT : file allocation table                         |    |

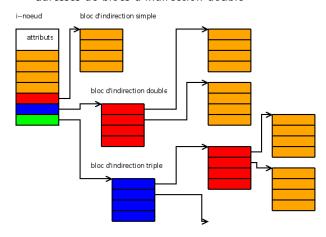

|   |      | 4.5.4 Tables des blocs Unix                               |    |

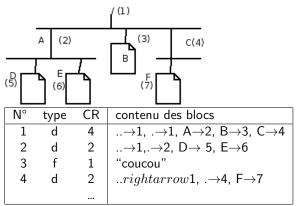

|   |      | 4.5.5 Représentation des répertoires                      |    |

|   |      | 4.5.6. Autres caractéristiques des SGE                    |    |

## Chapitre 1

## Ordinateurs et systèmes

### 1.1 Le premier ordinateur

Les ordinateurs tels que nous les connaissons sont des objets qui s'incrivent dans une longue suite d'inventions et de combinaisons de technologies diverses.

Si on définit l'ordinateur comme

un appareil électronique qui fait des calculs en suivant les instructions d'un programme enregistré

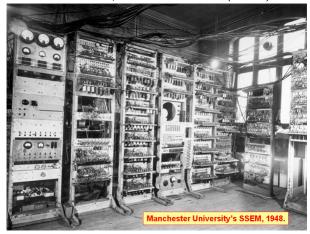

le premier ordinateur construit est très probablement le Manchester Small Scale Experimental Machine (SSEM)<sup>1</sup>,

qui a tourné pour le première fois le 21 juin 1948. Il avait été réalisé par Tom Kilburn et Geoff Tootill, dans l'équipe de Freddie Williams, professeur d'électrotechnique à l'Université de Manchester.

Voir le reportage tourné par la BBC en 1948, sur http://news.bbc.co.uk/2/hi/technology/7465115.stm

#### 1.1.1 Les calculateurs électroniques

Les calculateurs électroniques à programme existaient déjà depuis une quinzaine d'années, mais leurs programmes n'étaient pas enregistrés en mémoire. Ils étaient soit externes (bande ou carte perforées), soit figés. Par exemple sur l'ENIAC (1946), des interrupteurs à tourner dans tableau de connexion pour réaliser les 0 et les 1 d'une mémoire morte.

Cette manière de faire dérivait assez naturellement des machines à traiter les cartes perforées, utilisées depuis la fin du XIXe siècle.  $^2$

En réalité le SSEM était un prototype destiné à tester l'utilisabilité d'une mémoire à tube cathodique inventée par F. Williams.

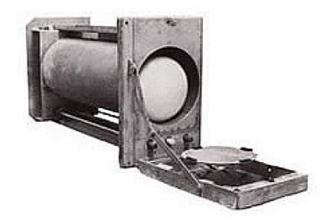

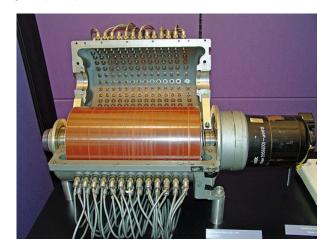

#### 1.1.2 Mémoire à tube de Williams-Kilburn

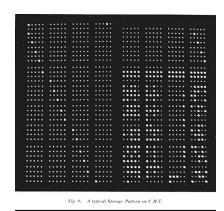

Cette innovation utilisait un tube d'oscilloscope standard, dans lequel un faisceau d'électrons permettrait d'allumer des points de phosphore sur l'écran, avec une certaine rémanence. Le tube de Williams-Kilburn utilise la propriété suivante : quand le faisceau bombarde un point de l'écran, des électrons secondaires sont éjectés par le phosphore, en quantité différente selon que le point est ou non déjà allumé. En mesurant la tension sur une plaque métallique devant l'écran, on peut connaître l'état du point.

En 1947, l'équipe de Williams avait réussi à stocker 2048 bits sur un écran pendant des heures, ce qui promettait une technologie de mémoire rapide, bon marché, basée sur des composants standards, destinée aux calculateurs.

L'idée est donc venue assez naturellement de fabriquer un calculateur simple avec une mémoire à tube pour en tester la fiabilité dans une machine qui effectue plusieurs milliers de lectures/écritures par seconde. Jusque là, le tube avait été testé en adressant les bits par un jeu d'interrupteurs manuels...

<sup>1.</sup> surnommé "Baby", voir http://www.computer50.org/mark1/new.baby.html

<sup>2.</sup> Voir l'article de Wikipedia consacré à la mécanographie

#### 1.1.3 Architecture et programmation

**L'architecture du SSEM** est très simple. En termes modernes, c'est une machine 32 bits, avec une mémoire de 32 mots de 32 bits (1024 bits stockés sur un tube), extensible à 8192.

Les calculs se font en nombre entiers en notation complément à deux.

Deux tubes étaient utilisés pour les registres spéciaux :

- l'un pour l'accumulateur A (32 bits) sur lequel se font les opérations

- l'autre pour CI (control instruction) qui contient d'adresse de l'instruction en cours, et PI (present instruction), l'instruction elle-même

Un dernier tube (sans plaque) dupliquait le premier, permettant de voir les bits en mémoire <sup>3</sup>.

La mémoire du SSEM

**Le jeu d'instructions** était réduit à 7 instructions d'un format unique : 3 bits pour le code opération, et 13 bits pour l'adresse S de l'opérande. les 16 derniers bits étaient inutilisés. Les 7 opérations étaient

- LDN S (load negative) A = Mem[S], qui charge dans l'accumulateur l'opposé du contenu d'un mot mémoire

- SUB S (subtract) A = A Mem[S], qui soustrait le contenu d'un mot

- STO S (store) Mem[S] = A, qui copie en mémoire le contenu de l'accumulateur

- CMP (compare) If A < 0, CI = CI + 1, qui saute l'instruction suivante si l'accumulateur est négatif,

- JMP S (jump) CI = Mem[S] + 1, qui provoque un saut indirect, à l'adresse contenue dans un mot de la mémoire.

- JRP S (jump relative) CI = CI + Mem[S] + 1, pour un saut indirect relatif.

- HLT (halt) qui arrête l'ordinateur.

Ce jeu d'instruction a été choisi parce qu'il était réalisable avec un minimum de circuits électroniques. Il ne simplifie évidemment pas la vie du programmeur. Par exemple, pour additionner deux nombres x et y situés aux adresses 20 et 21, il faut 4 opérations en passant par une variable temporaire (d'adresse 22)

```

0 LDN 20 ; A contient -x

1 SUB 21 ; A contient -x-y

2 STO 22 ; Mem[22] contient -x-y

3 LDN 22 ; A contient -(-x-y) = x+y

```

Voici un exemple plus complexe, écrit en utilisant des adresses symboliques : le calcul du maximum de deux nombres X et Y et le rangement dans Z.

```

# calculer la différence

```

```

0 LDN X; A = -x

1 STO TMP; TMP = -x

2 LDN TMP; A = x

3 SUB Y

```

```

# selon la différence, charger -X ou -Y

# dans l'accumulateur

```

```

4 CMP

5 JMP I8; si A positif

6 LDN Y

7 JMP I9

8 LDN X

```

# et envoyer l'opposé de l'accumulateur dans Z

```

9 STO TMP

10 LDN TMP

11 STO Z

12 HLT

```

# Les variables

= 42

= 15

13 X

18 i9

```

15 TMP = 0

16 Z = 0

# les adresses de saut

17 i8 = 7

```

Remarque : pour aller à l'instruction 9, l'instruction 7 charge le mot d'adresse 17 dans le CI, auquel il ajoute 1 comme après toute instruction. C'est pourquoi le mot 17 contient 8, l'adresse qui précède celle de l'endroit où le programme doit se poursuivre.

#### 1.1.4 Une démontration probante

Le programme précédent suffit à occuper plus de la moitié de la mémoire disponible sur le SSEM, qui n'a évidemment jamais servi à faire des calculs très complexes. Le clou du spectacle était un programme de 17 instructions <sup>4</sup> pour trouver le plus grand diviseur propre d'un nombre N, en essayant de le diviser successivement par N-1, N-2 etc., la division étant elle-même réalisée par soustraction successives.

<sup>3.</sup> les bits de poids fort sont à droite, contrairement à la notation habituelle des nombres en binaire

<sup>4.</sup> La légende de l'université de Manchester dit que c'est le seul programme que le professeur Williams ait jamais écrit.

Kilburn et Williams devant la console du SSEM

Il a fallu 52 minutes de calcul (et 3,5 millions d'opérations) pour établir que le plus grand facteur propre de  $2^{18}$  était  $2^{17}$ . Ce que tout le monde savait déjà évidemment. Sur l'écran phosphorescent, une puissance de deux est facile à lire : un point allumé sur une ligne éteinte.

Peu importe : l'objectif était de montrer que la mémoire était fiable : peu importe les calculs du moment que le résultat est correct après des millions d'opérations.

#### 1.1.5 Les suites

Un vrai ordinateur est sorti de ces travaux, *Manchester Automatic Digital Machine* (MADM), opérationnel en avril 1949, et qui a donné naissance aux machines du constructeur Ferranti.

Quant aux tubes de Williams, ils ont été utilisés comme mémoires dans quelques ordinateurs célèbres (UNIVAC 1103, Whirlwind, IBM 701, IBM 702 ...) avant d'être rapidement supplantés par les mémoires à tores de ferrite, qui ont dominé le marché pendant 20 ans de 1955 à 1975, avant d'être remplacées par les mémoires à semi-conducteurs que nous utilisons aujourd'hui.

### 1.2 Structure d'un ordinateur simple

Schématiqument, un ordinateur est composé

- d'un processeur, circuit électronique capable d'exécuter une à une (mais très vite) les instructions d'un programme

- d'une mémoire centrale, circuit qui sert à mémoriser les données et les programmes pendant leur exécution

- des périphériques : imprimante, carte réseau, carte graphique, disque dur etc. reliés par des contrôleurs d'interface.

Le rôle du Baby étant de tester la fiabilité des mémoires à tubes de Williams-Kilburn, il était dépourvu de périphérique.

Dans ce chapitre, nous présentons ces divers éléments de façon très simplifiée.

#### 1.2.1 La mémoire

Différentes technologies ont été utilisées pour réaliser les mémoires des ordinateurs : bascules bistables à base de tubes

(triodes), mémoires à tores de ferrite, à transistors, circuits intégrés etc.

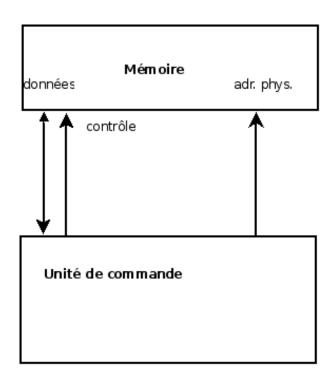

Indépendamment des technologies, la mémoire est un organe qui a pour fonction de stocker et restituer des "mots binaires" repérés par une adresse.

Les mots sont de taille fixe  $^5$ , par exemple l'ATLAS (réalisé en 1962 conjointement par l'université de Manchester, Ferranti et Plessey) avait une mémoire de 16384 mots de 48 bits. Les micro-processeurs des années 70 étaient souvent des machines à octets (mot = 8 bits), de nos jours ce sont des mots de 32 ou 64 bits.

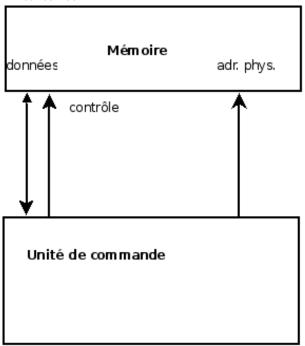

La mémoire communique avec le reste de l'ordinateur par 3 bus (groupes de fils)

- le bus de contrôle (il faudrait dire bus de commande), qui indique à la mémoire l'opération que l'on veut effectuer : lecture ou écriture;

- le bus de données, bidirectionnel, qui sert à émettre et recevoir les mots;

- le bus d'adresses, qui indique à la mémoire l'adresse concernée.

La mémoire et ses trois bus

#### **Opérations:**

- lecture : pour consulter l'adresse A en mémoire, le processeur place le nombre A sur le bus d'adresses, et envoie le signal de contrôle "lecture". Après un petit délai de réponse, le contenu du mot d'adresse A est présent sur le bus de données.

- écriture : pour envoyer un mot M à l'adresse A, le processeur place A sur le bus d'adresses, M sur le bus de données et active l'ordre d'écriture.

<sup>5.</sup> Il y a eu bien sûr quelques exceptions, qui ont été des échecs. Dans l'histoire des ordinateurs, beaucoup de choses ont été essayées.

Remarque: sur certaines machines (c'était le cas du processeur 8088 qui équipait les premiers PC d'IBM <sup>6</sup>), les bus de données et d'adresses sont *multiplexés*, ils partagent des fils. L'avantage est de minimiser le nombre de connexions entre circuits intégrés (et du nombre de pattes), l'inconvénient est que les données et les adresses ne sont pas être transmis en même temps, ce qui se fait au détriment des performances. Un signal de commande supplémentaire précise si l'information qui circule est une adresse ou une donnée.

#### 1.2.2 Le processeur

Un processeur est un dispositif électronique relativement simple, composé de circuits logiques divers. Il communique avec la mémoire (voir plus haut) et les périphériques par des bus de données, d'adresses, et de commande.

Son rôle est d'exécuter, les unes après les autres, des instructions qui sont stockées en mémoire.

#### Instructions et registres

Le **compteur de programme** <sup>7</sup> est un registre <sup>8</sup> qui contient l'adresse de la prochaine instruction à exécuter. C'est un *compteur* parce que, la plupart du temps, on va lui ajouter 1 pour passer à l'instruction suivante.

La première action du processeur est de lire en mémoire le mot qui contient cette instruction, et de la placer dans un **registre d'instruction**, où il sera décodé. <sup>9</sup>.

Par exemple, on aura peut être lu le mot de 32 bits 000110000100001100000000000101010 qui, sur un PowerPC 32 bits, se décompose en 001110 00010 00011 00000000 000101010 ce qui représente

- les 6 premiers bits : le code de l'opération "ajouter une constante"

- un numéro de registre destination (registre 2) sur 5 hits

- un numéro de registre source (registre 3)

- une constante (42) codée sur 16 bits

et qui signifie : ajoutez au registre de travail numéro 3 la valeur 42, et placez le résultat dans le registre 2, ce qu'on écrirait en *langage d'assemblage*

addi 2,3,42

L'exécution de l'opération ci-dessus fera appel à différents autres circuits

- les registres généraux, qui stockent des valeurs intermédiaires (il y en a 32 sur le PowerPC). C'est la généralisation de l'accumulateur A du SSEM.

- une **unité arithmétique**, qui sera ici chargée de s'occuper de l'addition.

Certaines opérations permettront des transferts entre registres et mémoire, par exemple

stw 5,0,1234

envoie (*store*) le contenu du registre général 5 à l'adresse 1234 de la mémoire.

Il y a également des instructions pour comparer le contenu de registres, et d'autres qui changent le cours de l'exécution si une condition est remplie, en indiquant le numéro de la prochaine instruction à exécuter.

En fait, les instructions de comparaison positionnent des indicateurs booléens dans un **registre de condition** qui mémorisent le résultat de la comparaison (inférieur, supérieur, égal?)

En fonction de ces indicateurs, les **instructions de branchement conditionnel** incrémentent le compteur de programme, ou lui affectent une autre adresse.

Rappel : sur le SSEM, le bit de signe de l'accumulateur était l'unique indicateur de condition, utilisé par l'instruction CMP.

À ces opérations s'ajoutent des **instructions d'entréesortie**, permettant le dialogue avec des circuits **contrôleurs de périphériques**, ainsi que des instructions spéciales que nous verrons plus tard.

Tous ces circuits fonctionnent sous le contrôle d'un **séquenceur**, qui enchaîne les différentes étapes :

- envoyer le contenu du PC sur le bus d'adresse, et un ordre de lecture

- copier la valeur présente sur le bus de données dans le registre d'instruction RI, et indiquer la fin de lecture

- décoder l'instruction contenue dans le RI

- l'exécuter. Si il s'agit de "ajouter 42 au registre 3" :

- envoyer le contenu du registre 3, la valeur 42 et l'ordre d'addition l l'unité arithmétique (circuit de calcul)

- copier le résultat dans le registre 3

- ajouter 1 au PC

- et recommencer

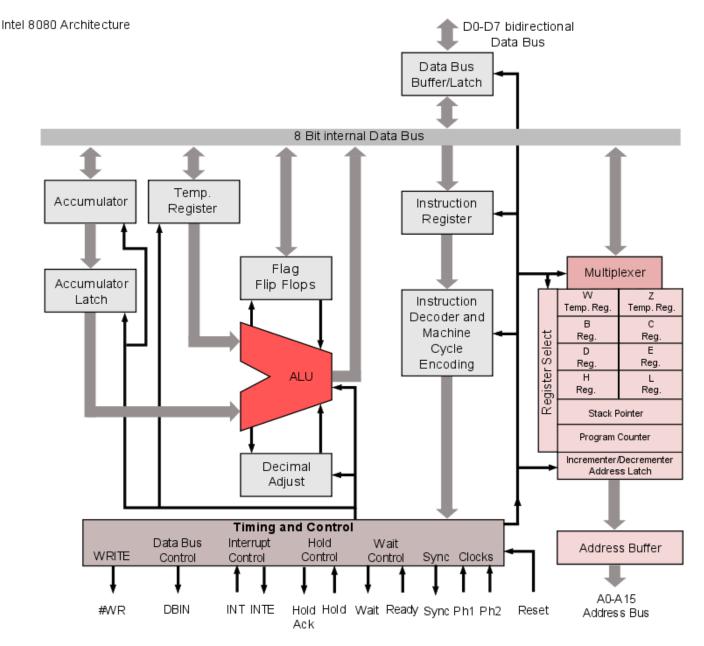

#### Architecture interne d'un processeur

Le schéma ci-dessous montre l'architecture interne du processeur 8080 mis sur le marché par Intel en Avril 1974. C'est le second micro-processeur 8 bit, après le 8008.

<sup>6.</sup> Le processeur 8086 d'INTEL possédait des bus séparés, le 8088 qui en était dérivé était à la fois plus cher à fabriquer (c'est un 8086 avec en plus des circuits de multiplexage/démultiplexage) et moins performant. Ceci dit, le 8086 nécessitait une famille de circuits associés 16 bits (contrôleurs d'interruption, etc), alors que le 8088 pouvait se contenter des circuits 8 bits qui étaient déjà produits en masse pour les microprocesseurs 8080 et 8085 qui équipaient les micro-ordinateurs les plus courants de l'époque (sous CP/M).

<sup>7.</sup> ou pointeur d'instruction, compteur ordinal...

<sup>8.</sup> en électronique numérique, un *registre* est un circuit qui mémorise quelques bits d'information. Il est possible d'y charger une valeur, et de la relire ensuite.

<sup>9.</sup> La terminologie du SSEM les désignait par CI (current instruction) et PI (present instruction)

#### On retrouve

- en haut, le bus de données de 8 bits

- en bas à droite le bus d'adresse 16 bits,

- à gauche l'accumulateur A

- au centre l'unité arithmétique et logique (ALU)

- le registre d'instruction

- à droite une "banque de registres", dont le compteur de programme, et des registres de travail (B,C,D ...)

#### Le modèle du programmeur

Dans un ordinateur, certains registres sont utilisable directement par le programmeur (comme le registre accumulateur par exemple), et d'autres ont un rôle interne (le registre d'instruction).

Ce qu'on appelle **modèle du programmeur**, c'est la partie qui est utilisable directement par le programmeur

- le compteur de programme,

- les registres généraux et spécialisés

- les registres de condition

- les différentes catégories d'instruction

- chargement/ rangement en mémoire

- arithmétique

- logique : et, ou, décalages...

- tests

- branchements conditionnels et inconditionnels,

- ...

Par exemple, dans le 8080, le registre C est utilisable comme opérande d'une instruction, par exemple MOV A,C (copie de C dans A), il fait donc partir du modèle contrairement au registre TEMP qui sert d'intermédiaire dans cer-

taines instructions. Par exemple l'instruction ADD B (ajouter le contenu du registre B à l'accumulateur) se déroule en deux temps

- copier B dans TEMP, et A dans le registre "latch" (autre registre temporaire), pour les présenter en entrée de l'UAL,

- 2. envoyer le résultat de LATCH+TEMP, sortant de l'UAL, dans A.

**Exercice 1.** Pourquoi y a-t-il deux étapes, et non une seule?

#### La programmation en langage machine

Un exemple de programme en pseudo-assembleur vous montre le niveau de détail auquel il faut descendre quand on programme dans un *langage machine* : la séquence ci dessous, qui commence à l'adresse 100, calcule la somme des entiers de 1 à N, en supposant que N est dans le registre 3 et que le résultat doit aller dans le registre 4.

```

100 mettre la valeur 0 dans r4

101 comparer r3 et la valeur 0

102 si égal, aller à 106

103 ajouter r3 à r4

104 ajouter la valeur -1 à r3

105 aller à 101

106 ...

```

Après l'exécution de l'instruction d'adresse 102, le compteur de programme vaudra 103 ou 106, selon la valeur des indicateurs positionnés par l'instruction précédente (101).

**Exercice 2.** Écrivez un programme du même type pour le SSEM, en essayant de le faire tenir sur 32 mots.

Comme vous le voyez, un processeur n'est pas bien compliqué. C'est un assemblage de quelques circuits de base : registres, additionneurs, etc. qui sait exécuter des instructions de base très élémentaires.

Ce qui est compliqué c'est de combiner des instructions aussi rudimentaires pour effectuer des traitements utiles (qui ne sont pas forcément simples, eux). Affronter cette complexité, c'est la spécificité du travail du programmeur.

#### 1.2.3 Les périphériques

Enfin, dès les années 60, une grande variété de périphériques permet l'entrée, la sortie et le stockage des données, ainsi que la communication.

Sur les premiers ordinateurs, les périphériques courants étaient

- les lecteurs de rubans perforés, support fragile et peu commode hérité des téléscripteurs, abandonnés rapidement.

- Les lecteurs et perforateurs de cartes (hérités de la mécanographie),

- les imprimantes;

- les lecteurs de bandes magnétiques.

- des terminaux interactifs : machines à écrire électriques, voire écrans cathodiques.

Assez rapidement, on en est venu à utiliser un petit ordinateur auxiliaire - dit "frontal" - pour recopier les cartes perforées sur des bandes magnétiques, de lecture bien plus rapide. Et inversement, les résultats de l'ordinateur principal étaient transférés sur des bandes magnétiques que le frontal se chargeait de faire imprimer ou perforer.

Ainsi on économisait le temps précieux du gros ordinateur.

#### 1.2.4 Les outils de programmation

Dans les premiers temps de l'informatique, le programmeur écrivait ses programmes en binaire, en utilisant la liste des instructions de l'ordinateur (instruction set) et en les codant lui même en binaire. Pour des programmes de quelques dizaines d'instructions, c'était encore envisageable.

Il est ensuite apparu que cette activité de codage, éminemment fastidieuse, était trop sujette à erreurs. Il était donc préférable d'utiliser un programme pour faire mécaniquement ce codage sans risque d'erreur.

L'histoire officielle dit que l'idée d'utiliser un programme de traduction vient de John Neumann en 1945, mais selon d'autres sources <sup>10</sup>, Von Neumann était en fait initialement opposé à cette idée (émise par un étudiant), parce que cela gaspillait le précieux temps de calcul de l'ordinateur, alors qu'on pouvait très bien confier ce travail à des étudiants modestement rémunérés.

Un programme écrit en *langage d'assemblage* se présente comme une suite d'instructions utilisant les codes mnémoniques, comme addi pour "add immediate value" sur le PowerPC. Parfois c'est plus obscur, comme lwzxu (load word with zero indexed with update). L'assembleur est le programme de traduction <sup>11</sup>, qui assemble les traductions de chaque instruction.

On est ensuite passé (au milieu des années 50) à la traduction automatique de formules mathématiques, puis de programmes complets, avec le langage FORTRAN (Formula translator). Là aussi, l'intérêt n'était pas évident pour tout le monde. Le même John Von Neumann a déclaré, quand on lui a présenté FORTRAN en 1954 « why would you want more than machine language? »

Inversement, l'arrivée de langages de haut niveau a parfois soulevé un enthousiame excessif. En effet, il suffisait d'écrire

multiply PRIX—UNITAIRE

by QUANTITE giving PRIX.

add PRIX to TOTAL.

<sup>10.</sup> https://beacon.salemstate.edu/~tevans/VonNeuma.htm

<sup>11.</sup> mais on dit souvent, par métonymie, "programmer en assembleur"

là où, autrefois, un professionnel barbu grassement rémunéré produisait des lignes de code absolument incompréhensibles

load PU mult QTE store PRIX add TOT store TOT

y compris par son chef de service, incapable d'en vérifier la qualité.

Quand COBOL a été annoncé au début des années 60, certains y ont vu, un peu vite, la fin du métier de programmeur.

C'était en effet la fin d'un certain type de programmation, mais il reste que même si le code est écrit avec des phrases anglaises et semble facile à relire après une formation d'une semaine, la difficulté est en réalité dans l'algorithmique et dans l'organisation du code, composé d'une multitude d'opérations simples. La programmation reste un métier à part entière, qui ne s'improvise pas.

#### 1.3 Utilisation en mono-tâche

Les faibles capacités des premiers ordinateurs (quelques dizaines de kilo-octets de mémoire) ne permettaient que de faire exécuter un programme à la fois.

Un opérateur était donc chargé de mettre le travail fourni par les utilisateurs (cartes perforées ou bande magnétique) dans la mémoire de la machine, de lancer l'exécution et de récupérer les résultats imprimés (ou enregistrer). Et de recommencer avec le travail suivant.

Chaque travail disposait donc de l'intégralité des ressources de la machine.

**Exercice 3.** Les premières machines, expérimentales, étaient utilisées en mono-tâche à la demande. Quand un utilisateur arrivait avec un travail à faire passer sur le calculateur, il devait attendre que les précédents aient libéré la place avant d'utiliser la machine.

Imaginons l'arrivée de 4 utilisateurs :

- John arrive à 8h00, avec un travail qui dure 40 mn

- Grace arrive à 8h10, avec un travail de 30 mn

- Alan arrive à 8h20, avec un travail de 1 h 5 mn

- Niklaus arrive à 8h40, avec un travail de 25 mn

- 1. Quel est le "temps de service" pour chaque utilisateur (durée entre son arrivée en salle d'attente et la fin de son travail), si ils passent dans l'ordre d'arrivée (politique FIFO, *first-in first-out*)? Calculez le temps de service moyen.

- Mêmes questions si les utilisateurs décident de faire passer en premier celui qui <sup>a</sup> a le travail le plus court (politique dite "du plus cours temps d'exécution").

- a. parmi ceux qui sont présents

#### 1.3.1 Moniteur d'enchaînement des travaux

Pour éviter de perdre du temps, on a vite eu l'idée d'automatiser l'enchaînement des travaux. Un petit programme, toujours présent en mémoire, assurait la lecture du travail suivant dès qu'un travail était terminé, et gagnait ainsi de précieuses minutes.

Cet embryon de système peut prendre la forme d'une boucle de quelques instructions pour copier en mémoire les cartes de l'exécutable à charger, avant de lui transférer le contrôle. Un programme utilisateur qui se termine normalement doit simplement relancer le moniteur.

En début de journée (et après chaque crash), l'opérateur manipule les interrupteurs de la console pour entrer ce "chargeur" en mémoire. Dans une version plus élaborée, c'est un dispositif électronique qui lit un ruban perforé contenant le chargeur : il suffit d'appuyer sur un bouton pour "recharger le chargeur".

Encore mieux : le programme sur bande perforée peut servir à charger un système plus volumineux, depuis un autre périphérique plus rapide (bande, disque ou tambour magnétique). C'est ce qu'on appelle le **bootstrapping**, ou **amorçage** : la procédure de démarrage d'un ordinateur, qui comporte notamment le chargement du programme initial, et qui peut se faire en plusieurs étapes.

Ce programme résident comportait aussi des sousprogrammes (par exemple lecture-écriture sur bande magnétique, sur disque etc.) qui pouvaient être appelés par les programmes des utilisateurs, et qu'il n'était donc pas nécessaire de recharger avec chaque travail.

<sup>12.</sup> Du moins présentées comme telles par le Directeur Informatique, qui trouve là un moyen d'asseoir sa position stratégique dans l'entreprise en négociant sa collaboration avec d'autres Directeurs..

#### 1.3.2 Planification de travaux

Dans les entreprises, des informaticiens étaient chargés de la planification de l'exploitation : un certain nombre de travaux devaient "passer" sur l'ordinateur, à eux de décider quand et dans quel ordre, en tenant compte de diverses contraintes :

- la taille mémoire de chaque programme, et celle de la machine,

- les périphériques utilisés : sur une installation à 3 lecteurs de bandes, on ne peut pas faire tourner en même temps 2 programmes qui ont chacun besoin de 2 lecteurs.

- les priorités définies par l'entreprise <sup>12</sup>

et en optimisant à la fois la satisfaction de chaque service demandeur, et la rentabilisation des matériels.

**Exercice 4.** Soit une installation avec un ordinateur mono-tâche. A partir de 8h00, on doit faire passer trois travaux A, B, C qui durent respectivement 1h, 30 min, et 45min. Et les utilisateurs sont évidemment pressés d'obtenir les résultats.

Quel est le temps d'attente moyen des utilisateurs si on les fait passer dans cet ordre sur l'ordinateur (monotâche). Dans l'ordre inverse ? Quel est l'ordre optimal ?

#### 1.3.3 Modifications matérielles nécessaires

Malheureusement, la coexistence en mémoire du "superviseur" et du travail utilisateur introduit de nouveaux problèmes. En effet, un programme utilisateur "buggé" (intentionnellement ou pas) peut

- altérer la partie de la mémoire réservée au superviseur, conduisant au plantage de la machine

- utiliser de façon incorrecte les instructions d'entréssorties (accès illégaux à des fichiers, périphériques endommagés, etc.)

Ceci a conduit à quelques modifications du processeur, suggérées dès la fin des années 50

- le processeur possède deux modes de fonctionnement "maître" (ou superviseur, ou privilégié) et le mode "esclave" (normal). Ceci est matérialisé par une bascule 1 bit.

- le superviseur s'exécute en mode maître, et les programmes utilisateurs en mode esclave.

- en mode maître, le processeur a accès à toute la mémoire, et peut exécuter toutes les instructions de la machine.

- en mode esclave, la zone mémoire accessible par le processeur est restreinte : deux registres indiquent le début de cette zone, et sont constamment comparés avec le compteur ordinal.

- en mode esclave, certaines instructions (par exemple les instructions d'entrée-sortie directes) ne peuvent par être exécutées <sup>13</sup>.

- Quand un programme viole ces règles d'accès, une exception se produit : le contrôle est rendu au superviseur, à une adresse fixée au départ. Le superviseur examine donc la situation et décide des suites à donner (reprendre le programme, y mettre fin etc).

- pour appeler les sous-programmes du superviseur, un programme utilise une instruction spéciale ("syscall", trap logiciel, ...), qui provoque aussi une exception. Le superviseur se charge alors d'effectuer (en mode privilégié) l'opération demandée, avant de rendre la main au programme appelant.

- Quand une exception se produit, le contenu du compteur de programme est automatiquement sauvegardé, soit dans une pile en mémoire, soit dans un registre spécial. Ceci permet de reprendre éventuellement l'exécution là où elle en était arrêtée

#### 1.3.4 Déroulement d'un appel système

**Point de vue du programmeur d'application** Par exemple, sous MS-DOS, pour faire afficher une chaîne de caractères il fallait

- placer le nombre 9 dans le registre AH

- placer l'adresse de la chaîne dans la paire de registres DS :DX

- appeler l'instruction INT 21H

**Déroulement** L'exécution de l'interruption 33 (21H) déclenche l'appel au système d'exploitation, dans la **routine** de traitement de l'interruption 21H. Ce sous programme consulte le registre AH qui indique la fonction demandée : 9 = affichage d'une chaîne. Une fois cette fonction affectée (par copie de caractères dans la mémoire de l'écran), le système place le code de retour 24H (36) dans le registre AL, et rend la main au programme utilisateur.

# 1.4 Profiter des temps morts : la multiprogrammation

#### 1.4.1 Motivation économique

A l'époque (début des années 60) les ordinateurs coûtent une fortune, on essaie donc de les rentabiliser au maximum.

Les machines sont composées d'une unité centrale (processeur et mémoire) et de périphériques : lecteurs de cartes perforées, de bandes, imprimantes etc. Or on observe que les opérations d'entrées-sorties sont extrêmement lentes par rapport aux possibilités d'un processeur.

Prenons par exemple le Gamma 60 dont le premier exemplaire a été livré par la société Bull à la SNCF en 1958, avec 6 imprimantes et 16 dérouleurs de bande, il occupait  $360m^2$ .

<sup>13.</sup> Dans le Stretch d'IBM, les ingénieurs avaient oublié de rendre privilégiée l'instruction qui permet de passer en mode maître. Doh!

#### Pour les périphériques :

- le lecteur de ruban fonctionnait à 300 caractères par seconde

- les cartes perforées de 80 colonnes étaient lues à 300 cartes/mn

- les imprimantes fonctionnaient à 300 lignes par minute

et une instruction (opération sur nombres de 10 chiffres) prenait de 100 à 500 microsecondes, soit des dizaines de milliers par seconde.

Dans ces conditions, il est clair que le processeur est le plus souvent en attente d'une E/S.

L'idée est donc de faire cohabiter plusieurs tâches dans la mémoire : quand la tâche "active" demande à lire des cartes sur le lecteur, on met à profit le temps libre du processeur pour faire avancer une autre tâche.

#### 1.4.2 Étude d'un cas

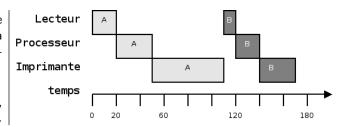

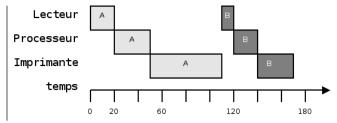

Imaginons deux tâches A et B :

- la chargement de A depuis le lecteur de cartes dure 20 secondes, elle fait du calcul pendant 30 secondes, et l'impression des résultats prend 1 minute;

- le chargement de la seconde B dure 10 secondes, son calcul 20 secondes et l'impression 30 secondes.

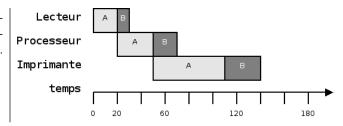

Le graphique ci-contre montre ce qui se passe sous le contrôle d'un "moniteur d'enchaînement de travaux". La tâche B n'est chargée en mémoire que quand A s'est terminée (t=110s) et se termine à t=170s.

Le processeur a travaillé 30+20=50s soit un taux d'occupation de 50/170=29,4%

#### Exercice 5.

- calculez le taux d'occupation du lecteur de cartes

- calculez le taux d'occupation de l'imprimante.

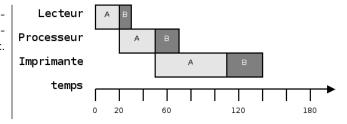

Voici maintenant le déroulement dans un système multitâche; la tâche B est chargée dès que le lecteur a été libéré, puis est exécutée quand le processeur est libre, etc.

#### Exercice 6.

- Calculez les taux d'occupation, comparez avec les chiffres précédents.

- Même question si on commence par exécuter B au lieu de A.

- Imaginons qu'il s'y ajoute une troisième tâche C semblable à B. Représentez le déroulement dans les deux cas (enchaînement séquentiel et multitâche). Comparez les chiffres.

#### 1.4.3 La mise en oeuvre du multitâche

Pour mettre en oeuvre efficacement le multitâche, il faut que le processeur ne soit pas bloqué en attente des opérations d'entrée-sorties, qui doivent se dérouler en parallèle avec les calculs.

On confie donc le pilotage de périphériques à des circuits spécialisés, à qui le processeur enverra des commandes (requêtes d'E/S), et qui préviendront le processeur, par un **signal d'interruption**, quand la requête est terminée. Les interruptions sont traitées comme les exceptions vues plus haut.

Le fonctionnement par interruption décharge ainsi le processeur de la surveillance des périphériques, qui peut consacrer son temps à l'avancement des autres tâches.

L'idée des interruptions est apparue en 1955. La NASA possédait un Univac 1103 pour ses besoins de calculs scientifiques (traitement de données d'essais en tunnel de soufflerie avec Boeing) et ses applications administratives. <sup>14</sup>

Le programme de collecte de données était chargé en mémoire et présent pendant que les applications de gestion tournaient. Quand les tests en soufflerie étaient prêts, un bouton poussoir situé dans le hangar permettait d'activer le programme "instantanément" <sup>15</sup> : le contenu des différents registres de l'ordinateur (compteur ordinal, conditions, ...) était alors sauvegardé et le contrôle était transféré au programme de collecte de données.

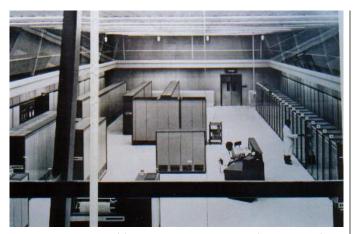

# 1.5 Fonctionnement d'un centre de calcul

Les premiers systèmes multi-tâches sont toujours destinés au traitement par lots (batch processing), mode d'exploitation qui est assez similaire à 'enchaînement automatique des travaux décrit plus haut : on "enfourne" dans la machine une suite de travaux à réaliser, qui ressortent une fois terminés.

La différence, c'est qu'avec le multitâche, le travail N+1 peut être chargé en mémoire avant que le travail N ne soit terminé : on charge autant de programmes que possible pour remplir la mémoire, pour avoir un meilleur rendement et ne pas gaspiller le temps du processeur. Ils ne se terminent pas forcément dans l'ordre où ils ont commencé.

Dans les années 70, les étudiants en informatique de Bordeaux 1 travaillaient de la façon suivante

- 1. il fallait d'abord écrire le programme sur le papier

- 2. puis se rendre dans une salle où se trouvaient quelques perforatrices comme l'IBM 29 :

(source : http://www.math-cs.gordon.edu/ courses/cs323/FORTRAN/keypunch.html)

pour transcrire le programme sur des cartes perforées <sup>16</sup>. Chaque carte contenait une ligne de 80 caractères.

3. les cartes, entourées par un élastique, étaient placés dans un bac qu'un étudiant (rémunéré) allait porter au Centre de Calcul Interuniversitaire, où se trouvait l'ordinateur IRIS 80, trois ou quatre fois par jour. Les bacs de cartes étaient alors confiés à un opérateur, qui les plaçait dans le lecteur de cartes, lançait le traitement et récupérait (bien plus tard) les cartes avec les listings de résultats.

<sup>6.</sup> Column indicator

8. Program control lever

7. Punched card stacker

5. Pressure plate

9. Reading station

10. Backspace key

11. Insert slots for cards to be duplicated

12. Keyboard

3. Punching station

2. Function switches

<sup>14.</sup> http://www.cs.clemson.edu/~mark/interrupts.html

<sup>15.</sup> la solution précédente consistait à réserver l'utilisation de l'ordinateur à l'avance, et à téléphoner à l'opérateur pour qu'il lance le programme le moment donné

<sup>16.</sup> avec 4 perfos, il fallait évidemment faire la queue, un peu moins la nuit et le week-end

Source http://www.feb-patrimoine.com/projet/iris80/iris80.htm.

- 4. il en profitait pour ramener les travaux précédents, avec les listings de résultats.

- 5. en récupérant son travail, l'étudiant constatait généralement qu'il manquait un point-virgule quelque part : ne restait plus qu'à trouver où, remplacer la carte fautive, et remettre le paquet dans le bac de départ, pour avoir le résultat quelques heures plus tard.

Dans ces conditions, il était évidemment préférable de réfléchir avant de taper, et de se relire soigneusement plusieurs fois avant de mettre les cartes dans le bac...

Les étudiants de troisième cycle, et les chercheurs en mathématiques et informatique, disposaient quant à eux d'une petite salle avec quelques **terminaux conversationnels** hétéroclites: telex Olivetti, terminaux à écran cathodiques (HP 2621), clavier avec imprimante thermique, écran graphique Textronix 4027, reliées directement au centre de calcul par des lignes à 9600 bit/s. De quoi travailler très confortablement.

# 1.6 Travailler à plusieurs : le temps partagé

En effet un nouveau besoin est apparu avec l'utilisation de terminaux interactifs : telex transformés, machines à écrire électriques, et écrans alphanumériques. Au départ les utilisateurs peuvent soumettre de nouvelles tâches dans le traitement par lots, mais les programmes interactifs amènent une contrainte supplémentaire : chaque utilisateur doit avoir l'impression d'utiliser une machine "réactive" : si un collègue lance un programme de calcul lourd (quelques milliers de décimales de  $\pi$ )  $^{17}$ , ça ne doit pas empêcher les autres de travailler en monopolisant le temps du processeur.

C'est la prise en compte de cette contrainte qui conduit au *time sharing* : le temps du processeur est partagé "équitablement" entre les utilisateurs.

Parmi les premiers systèmes, le plus connu est CTSS (Compatible Time Sharing System) issu du projet MAC

(Multi Access Computer) de John McCarthy au MIT <sup>18</sup>. Ce système multi-utilisateurs (à partir de 1961, en production en 1964) tournait sur un IBM 7094 modifié, avec une mémoire de 2 fois 32K mots de 36 bits. Lire par exemple "The IBM 7094 and CTSS" par Tom Van Vleck, http://www.multicians.org/thvv/7094.html

A voir absolument: le reportage "1963 Timesharing: A Solution to Computer Bottlenecks" (27 minutes) sur http://www.youtube.com/watch?v=Q07PhW5sCEk, avec une longue interview de Fernando J. Corbato, responsable du projet, qui explique le fonctionnement du temps partagé, suivie par une démonstration.

Une démonstration plus courte http://www.youtube.com/watch?v=sjnmcKVnLiO (Robert Fano explains scientific computing), à partir de 5:20.

**Exercice 7.** Imaginons que 3 utilisateurs d'un système en temps partagé lancent en même temps des travaux qui nécessitent 10 minutes de calcul chacun.

- si ces travaux sont envoyés dans une file d'attente pour être traités un par un, le premier utilisateur aura sa réponse dans 10 minutes, le second dans 20 minutes, et le troisième dans 30, d'où un temps d'attente moyen de 20 minutes;

- 2. si ils se déroulent en temps partagé, ils dureront tous les trois 30 minutes.

Dans ce contexte, pourquoi les utilisateurs préfèrent-il quand même la seconde solution?

<sup>17.</sup> ou un programme qui boucle, comme ça arrive parfois.

<sup>18.</sup> John McCarthy, décédé en octobre 2011, est un des pionniers de l'informatique : systèmes d'exploitation, intelligence artificielle, programmation symbolique et fonctionnelle, etc. Lire sa biographie sur Wikipedia. Parmi ses articles, un mémo "A Time Sharing Operator Program for Our Projected IBM 709" daté du 1er janvier 1959. Voir ses souvenirs sur le time-sharing dans http://www-formal.stanford.edu/jmc/history/timesharing/timesharing.html

### 1.7 De nos jours...

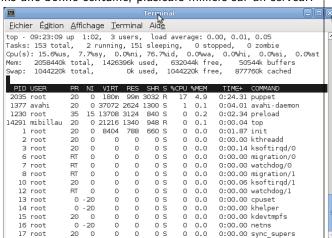

Les systèmes d'exploitation modernes <sup>19</sup> sont tous capables de faire exécuter plusieurs tâches en même temps. Sous Unix, la commande top vous permet de voir les tâches en cours : sur un ordinateur personnel vous constaterez qu'il en a au moins une bonne centaine, plusieurs milliers sur un serveur.

Les solutions qui permettent le fonctionnement en multitâches ont été trouvées, mises en place et généralisées, dès le début des années 60 : interruptions, partage de la mémoire, etc.

Dans les années 70 et 80, on a assisté à un recul ap-

parent : les premiers micro-ordinateurs étaient destinés à un usage personnel.

Les contraintes de coût qui ne permettaient qu'une faible capacité mémoire (dizaines ou centaines de kilo-octets) expliquent la réapparition, pendant une dizaine d'années, des systèmes mono-tâches, comme  $\mathsf{CP/M}$  (Kildall, 1977) et MS-DOS (1981).

**Exercice 8.** Avez-vous vraiment besoin d'un système multi-tâches, avec protection mémoire etc, dans votre smartphone?

<sup>19.</sup> à l'exception de quelques systèmes embarqués ou de super-calculateurs

## **Chapitre 2**

## Les processus

#### 2.1 Introduction

Les systèmes d'exploitation modernes sont tous capables de faire exécuter plusieurs tâches en même temps. Sous Unix, la commande top vous permet de voir les tâches en cours : sur un ordinateur personnel vous constaterez qu'il en a au moins une bonne centaine, plusieurs milliers sur un serveur.

Mais matériellement, un processeur ne peut exécuter qu'une instruction à la fois. Même si les ordinateurs possèdent plusieurs processeurs, on est loin du compte : il n'y a pas un processeur par programme. <sup>1</sup>

Le déroulement parallèle de ces tâches est donc une *illusion*: en réalité le processeur consacre un peu de temps "faire avancer" une tâche, puis passe à une autre etc. à tour de rôle. C'est la rapidité de cette alternance, quelques millisecondes par tâche, qui donne l'impression, à notre échelle, que tout avance en même temps.

Une des fonctions importantes d'un système multitâche est donc de gérer les *commutations de contexte* : il doit

- noter l'état de la tâche en cours (sauvegarde du contexte)

- choisir une des tâches (ordonnancement)

- la relancer dans l'état où elle était arrêtée (restaura-

tion du contexte)

#### 2.2 Histoire

#### 2.2.1 Multitâche

Les systèmes d'exploitation multi-tâches sont apparus très rapidement dans l'histoire de l'informatique.

- Ordinateur Gamma 60 de la société Bull, en 1958 http://fr.wikipedia.org/wiki/Gamma\_60.

- Ordinateur LEO III de la société Lyons, 1961.

La société Lyons regroupait une chaîne de restaurants, des hôtels et des activités dans l'alimentaire (biscuits). Grande utilisatrice de machines à cartes perforées pour sa gestion, elle a compris avant beaucoup d'autres l'intérêt des recherches qui étaient menées sur les calculateurs électroniques (EDSAC, à Cambridge). Elle a donc embauché un technicien radar, loin de son coeur de métier, <sup>2</sup> pour développer ses propres ordinateurs pour ses applications de gestion. Le LEO I (Lyons Electronic Office) est sorti en 1951, et d'autres modèles ont suivi qui ont été commercialisés hors de la société Lyons. <sup>3</sup>

<sup>1.</sup> Dans la suite du cours, pour simplifier, on considère des machines à un seul processeur. Avec plusieurs processeurs, il y a des complications intéressantes, mais les principes de bas sont les mêmes.

<sup>2.</sup> Ce n'est pas un cas isolé : Honeywell (spécialiste de la régulation de chauffage) et Boeing (avions) ont aussi fabriqué des ordinateurs. Et plus tard le premier micro-ordinateur a été fabriqué en France pour l'INRA (Institut National de Recherche Agronomique), le Micral en 1972.

<sup>3.</sup> Sur le site http://www.leo-computers.org.uk/ des anciens employés de LEO Computers, vous trouverez de nombreuses photos et descriptions (et même des enregistrements de l'ambiance des salles machine).

**L'objectif** du multi-tâches est évident : si plusieurs programmes s'exécutent en même temps, ils utilisent les divers périphériques en parallèle, ce qui rentabilise au mieux l'instal-

lation informatique : on augmente le nombre de programmes que l'on peut faire exécuter dans une journée d'utilisation.

#### 2.2.2 Exemple : intérêt du multi-tâches

Imaginons deux tâches A et B:

- le chargement de A depuis le lecteur de cartes dure 20 secondes, elle fait du calcul pendant 30 secondes, et l'impression des résultats prend 1 minute;

- le chargement de la seconde B dure 10 secondes, son calcul 20 secondes et l'impression 30 secondes.

Le graphique ci-contre montre ce qui se passe sous le contrôle d'un "moniteur d'enchaînement de travaux". La tâche B n'est chargée en mémoire que quand A s'est terminée (t=110s) et se termine à t=170s.

Le processeur a travaillé 30 + 20 = 50s, soit un taux d'occupation de 50/170 = 29,4%.

#### Exercice 9.

- calculez le taux d'occupation du lecteur de cartes

- calculez le taux d'occupation de l'imprimante.

Voici maintenant le déroulement dans un système multitâches; la tâche B est chargée dès que le lecteur a été libéré, puis est exécutée quand le processeur est libre, etc.

#### Exercice 10.

- Calculez les taux d'occupation, comparez avec les chiffres précédents.

- Même question si on commence par exécuter B au lieu de A.

- Imaginons qu'il s'y ajoute une troisième tâche C semblable à B. Représentez le déroulement dans les deux cas (enchaînement séquentiel et multi-tâches). Comparez les chiffres.

#### 2.2.3 Du batch au time sharing

**Traitement conversationnel.** Un nouveau besoin apparaît à la fin des années 50: avec l'utilisation de terminaux interactifs: telex transformés, machines à écrire électriques, et écrans alphanumériques. Chaque utilisateur doit avoir l'impression d'utiliser une machine "réactive": si un collègue lance un programme de calcul lourd (quelques milliers de décimales de  $\pi$ )<sup>4</sup>, cela ne doit pas empêcher les autres de travailler en monopolisant complètement le temps du processeur.

C'est la prise en compte de cette contrainte qui conduit au *time sharing* : le temps du processeur doit être partagé "équitablement" entre les utilisateurs.

## 2.2.4 Support matériel du multi-tâches : les interruptions

Pour être réalisé, le multi-tâche nécessite l'ajout de quelques quelques fonctionnalités techniques sur le matériel.

En particulier, il ne serait pas raisonnable de devoir interroger constamment les périphériques pour savoir si les opérations qu'on leur a confiées (et qui sont attendues par certaines tâches) sont terminées ou non. Cette *boucle d'attente active* consommerait beaucoup de temps du processeur, temps que

<sup>4.</sup> ou un programme qui boucle, comme ça arrive parfois.

l'on souhaite consacrer à l'exécution de programmes "utiles".

L'ordinateur comporte donc des circuits spécialisés (contrôleurs de périphériques, en terminologie moderne) à qui le processeur confie l'exécution des entrées-sorties. Quand l'opération est terminée, le contrôleur envoie une interruption, signal électrique qui provoque le déroutement vers une "routine de traitement de l'interruption" située à une adresse convenue.

Dans un ordinateur multi-tâches, les interruptions "réveillent" le système d'exploitation, qui peut alors débloquer les tâches qui attendaient la fin de ces opérations.

D'autres mécanismes matériels sont également nécessaires pour la multiprogrammation, en particulier il faut *protéger l'espace mémoire de chaque tâche*, pour éviter qu'une autre tâche y accède indûment. La gestion de la mémoire fait l'objet d'un autre chapitre.

#### 2.2.5 Support logiciel

Avant la multiprogrammation, les systèmes d'exploitation étaient des *moniteurs d'enchaînement de travaux* assez très rudimentaires chargés au début de la mémoire au démarrage de la machine, et dont le rôle était simplement :

- de lire un programme exécutable (par exemple sur une bande magnétique) et de le copier un peu plus loin en mémoire.

- 2. de lancer son exécution,

- 3. et passer au suivant quand le programme s'est achevé.

Avec plusieurs tâches présentes simultanément, le système d'exploitation devient plus complexe : il doit traiter les interruptions provenant des périphériques, faire les commutations de contexte, gérer le partage de la mémoire, etc.

#### 2.3 Définitions

#### 2.3.1 Les processus

Le **processus** est une entité abstraite qui sert à représenter un **programme en cours d'exécution**.

Un processus regroupe :

- le code du programme : un espace mémoire contenant les instructions du programme;

- un espace mémoire pour les données de travail (variables, pile, tas);

- d'autres ressources : descripteurs de fichiers ouverts, des ports réseau, etc.

- des droits d'accès

Le noyau du système d'exploitation détient une **table des processus** qui décrit l'état des processus présents dans la mémoire

Pour chaque processus, il y a un **bloc de contrôle** (PCB, *process control block*) contient

- l'identifiant du processus

- son état : actif, prêt ou bloqué (voir plus loin)

- les valeurs des registres

- le compteur ordinal (numéro de la prochaine instruction à exécuter)

- ...

Ces informations donnent la "photographie" d'un programme au moment où il a été interrompu, et permettront de reprendre son exécution exactement là où il était arrêté, avec le même contenu dans chaque registre.

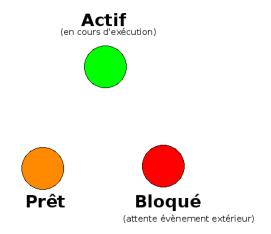

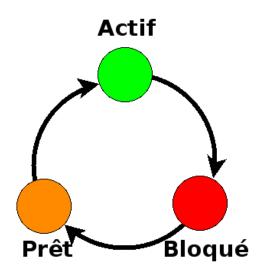

#### 2.3.2 Les états des processus

Trois états sont possibles pour un processus :

- actif quand le processeur est en train d'exécuter une de ses instructions. Dans un système monoprocesseur, un seul processus peut être actif à la fois;

- bloqué quand il est en attente d'un évènement, par exemple une lecture de données :

- **prêt** si il n'est ni actif ni bloqué.

#### 2.3.3 Changements d'état

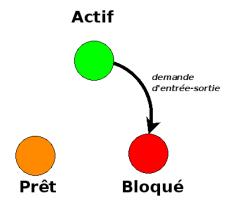

- Quand le processus actif a besoin de faire une opération d'entrée-sortie (E/S), il en fait la demande auprès du système d'exploitation par un "appel système" (sous Unix : read, write, etc.).

- Si il faut attendre la fin de cette opération pour continuer (par exemple pour une lecture), le système change l'état du processus, qui devient **bloqué**. On parle d'opération *bloquante*.

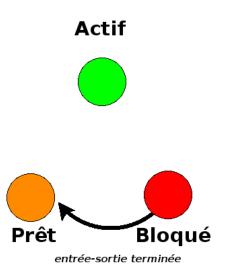

lorsqu'un périphérique signale au processeur qu'une opération d'E/S est achevée, le système d'exploitation "débloque" le processus qui attendait la fin de cette opération. Le processus est alors marqué comme prêt.

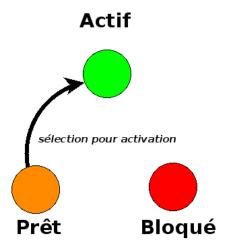

3. enfin, le système d'exploitation peut choisir un processus prêt pour le rendre **actif**.

Ce changement peut se faire quand le processus actif se termine ou se bloque, et "laisse sa place".

À un moment donné il peut y avoir plusieurs processus prêts : le choix du processus à activer est fait par un module appelé **ordonnanceur** (**scheduler**). Diverses **politiques d'ordonnancement** sont envisageables, nous les verrons en détail plus loin.

### 2.3.4 Multitâche coopératif

Dans un système multi-tâches dit "coopératif", les changements d'états d'un processus se font donc selon le cycle suivant, qui résume les transitions vues plus haut :

On observe que le processus qui est actif le reste tant qu'il ne demande pas d'opérations d'entrée-sortie.

Dans un tel système, Il est donc nécessaire que les programmes soient bien écrits pour

- ne pas boucler indéfiniment

- faire des entrées-sorties de temps en temps pour "bien se comporter" envers les autres processus et leur laisser des occasions de s'activer.

Évidemment ce genre de système marche assez mal en pratique. C'est ce qu'on trouvait dans Windows jusqu'à la version 3.11, et Mac OS jusqu'à MAC OS 9, plus de trente ans après l'invention du "vrai" multitâche!

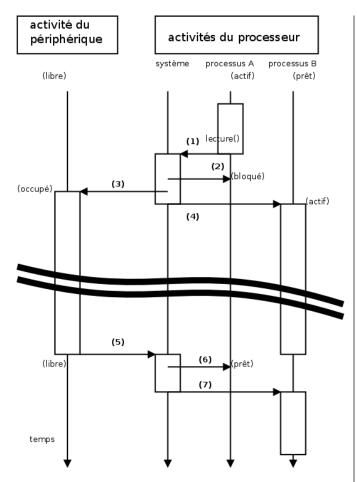

#### 2.3.5 Scénario détaillé

Le schéma ci-dessous montre le déroulement détaillé d'une opération d'entrée-sortie. On suppose qu'il y a au départ un processus A qui demande une lecture sur un périphérique inoccupé, et un processus B qui est prêt.

La scénario montre de haut en bas les "lignes de vie" des différentes activités : une pour le périphérique, et trois pour le processeur, pour distinguer ce qui relève du système, et des 2 processus.

Les flèches horizontales montrent les causalités.

- 1. A fait un appel au système d'exploitation pour demander une lecture.

- 2. le système marque le processus A comme bloqué

- 3. il ordonne au périphérique de se mettre au travail

- 4. il active B

- 5. le périphérique signale la fin de l'opération

- 6. l'interruption rend la main au système d'exploitation, qui marque A comme prêt

- 7. le système rend la main au processus B

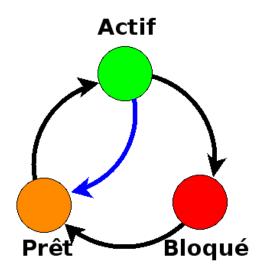

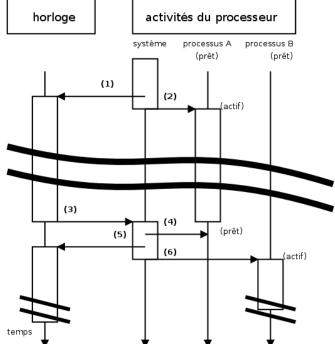

#### 2.3.6 Multitâche préemptif

Le multi-tâches préemptif, qui traite correctement les problèmes de partage du temps, a été proposé très tôt par McCarthy et Teager. Dans un papier de 1959, McCarty écrit que "l'idée n'est pas vraiment nouvelle".

En fait, il suffit d'ajouter un circuit d'horloge qui envoie une interruption au bout d'un certain délai. Quand le système active un processus, il programme cette horloge pour un certain **quantum de temps**. Il peut alors se passer deux choses

- soit le processus actif fait un appel système pour faire une E/S ou se terminer, et donc il "passe la main", au moins provisoirement, au système d'exploitation.

- soit il fait uniquement du calcul, et se trouve donc interrompu, automatiquement, par le signal d'horloge quand le quantum de temps est épuisé. Le processus est alors marqué comme prêt.

C'est ce qu'on appelle une **préemption**, capacité pour le système d'exploitation d'interrompre une tâche en cours pour activer une tâche plus prioritaire. Notez que ceci n'interdit pas que le processus ainsi préempté soit aussitôt réactivé, si l'ordonnanceur détermine qu'il est le plus prioritaire.

Vu autrement, voici le déroulement d'une préemption, à partir du moment où l'ordonnanceur a déterminé qu'il fallait activer le processus A :

- 1. le circuit d'horloge est armé pour un quantum de temps fixé

- le processus A est activé, et se met à faire du calcul "indéfiniment"

- le quantum est épuisé, l'horloge envoie une interruption

- 4. le système reprend la main

- 5. le processus A est marqué "prêt"

- 6. le processus B est choisi et activé, l'horloge est armée.

Dans ce système dit "multi-tâches préemptif" on a donc la garantie que le système d'exploitation reprend la main régulièrement, ce qui lui donnera l'occasion de distribuer le temps équitablement entre les processus non-bloqués, sans laisser un processus actif monopoliser le processeur.

Le multitâche préemptif est présent sur tous les ordinateurs multitâches depuis les années 60. On mesure donc à quel point, pendant la décennie 1980-1990, les principaux systèmes pour micro-ordinateurs (Windows et MacOS) étaient littéralement préhistoriques.

En effet, ces petits systèmes ont revécu, trente ans plus tard, l'histoire de l'informatique :

- au départ, petites machines à capacité très limitées

- utilisées par un seul programme à la fois, une seule personne à la fois. Dans le cas de la microinformatique, l'objectif commercial était de vendre un ordinateur par personne, surtout pas de le partager à plusieurs!

L'évolution vers le multi-tâche a été forcée par l'utilisation d'interfaces graphiques (si on a un multi-fenêtrage, on veut fatalement y faire tourner plusieurs programmes). Le multi-tâche coopératif est assez facile à réaliser par modification d'un système mono-tâche. Par contre le passage au multi-tâche préemptif nécessitait une refonte complète du système, ainsi que du catalogue d'applications. <sup>5</sup>

## 2.3.7 Multitâche préemptif et utilisation interactive

Soient deux utilisateurs X et Y d'un ordinateur en tempspartagé. Ils lancent tous les deux, à peu près en même temps, un programme qui fait une minute de calcul.

- Dans le cas d'un système coopératif, le calcul de l'un sera effectué pendant une minute, et alors commencera le calcul du second.

- Dans un système préemptif, les deux calculs alterneront par petites tranches correspondant au quantum de temps (valeurs courantes entre 1/50 et 1/1000 de seconde). Ils finiront donc tous les deux au bout de deux minutes.

En résumé, dans le cas coopératif, l'attente moyenne des deux utilisateurs sera  $\frac{60+120}{2}=90s$ , et avec le système coopératif  $\frac{120+120}{2}=120s$ .

**Exercice 11.** L'attente moyenne est-elle un bon critère pour mesurer la satisfaction des utilisateurs d'un système en temps partagé? Pouvez-vous proposer mieux?

### 2.3.8 Interruptions et multitâche, en résumé

Une interruption est un signal qui détourne le processeur de sa boucle d'exécution normale (lire une instruction, l'exécuter, passer à la suivante), pour effectuer un traitement particulier (routine de traitement d'interruption).

Les interruptions sont causées par

- les **périphériques** (fin d'exécution de requête)

- des signaux d'horloge

- des évènements extérieurs

- déroutements en cas d'erreur (accès illégal à la mémoire, division par zéro ...)

- interruptions logicielles provoquées par instruction spéciale

Dans un système d'exploitation multitâches, les interruptions sont traitées par le système, qui agit sur l'état des processus :

- venant d'un périphérique d'E/S : le système fait passer le processus demandeur à l'état prêt;

- venant de l'horloge (épuisement du quantum de temps), le système fait passer le processus actif à l'état prêt;

- interruption d'erreur (division par zéro etc) : le processus actif est supprimé.

### 2.4 Politiques d'ordonnancement

#### 2.4.1 Ordonnanceur

Dans un système d'exploitation multi-tâches, l'**ordonnanceur** (*scheduler*) est un composant du noyau, qui a pour fonction de choisir un des processus prêts pour l'activer

L'ordonnanceur applique une **politique d'ordonnancement**, algorithme ou heuristique qui est censé donner "de bons résultats".

#### 2.4.2 Critères d'évaluation

Une politique d'ordonnancement peut être évoluée selon plusieurs critères. On peut en effet souhaiter avoir

- **équité** : chaque processus dispose d'une part équitable du temps global,

- aucun n'est empêché de tourner (par exemple par une coalition de processus prioritaires)

- minimiser le temps de réponse : les utilisateurs interactifs souhaitent un système "réactif". Quand ils lancent des commandes courtes, la réponse doit être rapide.

- minimiser le temps d'exécution : les commandes longues ne s'éternisent pas.

- **maximiser le rendement** : on peut lancer davantage de travaux dans la journée.

<sup>5.</sup> On le sait assez peu, mais la société Microsoft prévoyait, après le lancement de DOS 3.0, de faire évoluer son catalogue vers Xenix, un système UNIX dont elle avait acheté les droits à ATT à la fin des années 70 de façon à pouvoir enfin remplacer DOS par un vrai système multitâches. Ce plan a été abandonné vers 1985, quand Microsoft et IBM ont commencé à développer ensemble OS/2 (nom de code "CP/DOS") qui devait préserver la compatibilité avec les applications existantes. En effet, commercialement, il est mal avisé de forcer les clients à racheter tout leur parc logiciel pour bénéficier d'un nouveau système, fut-il techniquement bien meilleur. La stratégie OS/2 a aussi été abandonnée au profit du développement de Windows NT, qui regroupe en fait les versions Windows 2000, XP, 2003, Vista, Home Server, Server 2008, et Windows 7.

Mais malheureusement

- ces objectifs sont contradictoires,

- le comportement des processus ne peut pas être prévu

Il n'y a donc **pas de politique optimale** valable dans tous les cas. On se contente d'**heuristiques**, dont l'expérience montre qu'elles fonctionnent bien (ou pas) dans des contextes voisins.

Qui plus est, pour chaque méthode il sera souvent possible de construire un "scénario pathologique" pour lequel les choses se passent mal, du point de vue d'un critère particulier. La difficulté est d'évaluer la probabilité avec laquelle de tels cas peuvent se produire, dans le contexte d'utilisation visé, ainsi que les conséquences.

Que des programmes d'affichage puissent "lagger" quelques secondes de temps en temps n'a pas la même importance pour une animation en flash dans un navigateur, et sur une console d'aiguilleur du ciel.

#### 2.4.3 Tourniquet

L'algorithme du **tourniquet** (synonymes : *round robbin*, FIFO, premier arrivé-premier servi, ...)

#### Principe:

- le système détient une liste des processus prêts;

- on choisit, pour l'activer, le premier processus de la liste;

- à la fin de son quantum de temps, un processus actif est placé en fin de liste

**Propriétés** : cette heuristique garantit une **équité** entre les processus, qui ont tous une occasion de tourner.

**Exercice 12.** Soit trois processus A, B et C à comportements périodiques : ils font du calcul, une opération d'E/S et recommencent (un très grand nombre de fois).

- Pour A le calcul dure 10 ms, 10 ms pour B, et 45 ms pour C

- une opération d'E/S de 20 ms

Étudiez le déroulement pendant les 150 premières ms

- pour un ordonnancement circulaire (tourniquet) sans réquisition

- pour un ordonnancement avec réquisition (quantum 20 ms)

Comparez les taux d'utilisation des CPU dans les deux cas.

#### 2.4.4 Priorités

Les priorités permettent de favoriser certains travaux.

On affecte un niveau de priorité (numérique) à chaque processus. Sous Unix, ce sont les numéros faibles qui sont les plus prioritaires.

#### Principe

- on choisit le processus de priorité la plus élevée

- si il y a plusieurs processus du même niveau, ils sont sélectionnés à tour de rôle (tourniquet)

#### **Propriétés**

il y a un risque de coalition : si il y a beaucoup de processus prioritaires qui font du calcul, ils occupent le temps du processus à eux seuls, empêchant les autres processus de tourner.

**Exercice 13.** Soient deux processus A, B au fonctionnement cyclique : ils font du calcul (durées  $d_a$ ,  $d_b$ ), une entrée-sortie (durée  $d_{es}$ ), et recommencent. Un processus C, moins prioritaire, ne fait que du calcul.

À quelle condition apparaît-il une coalition entre A et B qui empêche C de s'exécuter?

**Exercice 14.** Soient trois processus A, B et C, qui ont un comportement répétitif : ils font un peu de calcul pour une durée t (respectivement 10ms, 15ms et 45ms), puis une opération d'entrée-sortie (qui dure 20ms), et recommencent. Le processeur d'entrées-sorties traite les requêtes séquentiellement, dans l'ordre où il les reçoit.

- En supposant un ordonnancement par tourniquet sans réquisition, évaluez le taux d'occupation de la CPU, et du processeur d'entréessorties. Étudiez l'équité de l'ordonnancement.

- 2. Même question, avec un ordonnancement préemptif avec tourniquet, et un quantum fixé à 20 ms.

- Même question, avec un ordonnancement préemptif avec priorités (dans l'ordre décroissant B, A, C), et un quantum fixé à 20 ms.

#### 2.4.5 Priorités variables

En pratique on utilise des systèmes avec des priorités variables.

Exemple d'un tel système :

- chaque processus se voit accorder une priorité initiale (qui peut dépendre de l'utilisateur)

- la priorité baisse chaque fois que le processus termine son quantum de temps

- elle revient à son niveau initial après chaque entréesortie.

#### Ainsi

- les processus qui font beaucoup de calcul sont pénalisés, leur priorité baisse.

- les processus courts sont favorisés, ce qui donne aux utilisateurs interactifs une impression de réactivité.

de même les processus qui font beaucoup d'E/S (et donc chargent peu le processeur), ont davantage d'occasions de tourner.

**Exercice 15.** Au département informatique nous avons eu un problème avec un système d'exploitation (SysVr4) qui remontait les priorités les processus qui faisaient des entrées-sorties.

Les étudiants devaient écrire du code pour afficher les requêtes d'une base de données, avec un algorithme du style

Dans ce code, les opérations sur la base de données communiquent par l'intermédiaire d'un "pipe" avec un processus qui accède effectivement aux fichiers de la base.

Certains étudiants ont inversé le test d'arrêt. Leur programme entrait donc dans une boucle de conversation avec l'autre processus, qui répondait immédiatement avec un code d'erreur différent de 100.

Quelles sont les conséquences pour les autres utilisateurs ?

#### 2.4.6 Files multiples

On définit des classes de processus

- à chaque classe correspond une liste (FIFO) de processus

- chaque classe est sélectionnée régulièrement

On décidera par exemple d'avoir 3 classes : A (prioritaire), B (normal), C (non prioritaire), à qui on accordera respectivement 50 %, 30 % et 20 % du temps de calcul. Chaque classe sera gérée selon le principe du tourniquet,

Par exemple, pour les 5 premières activations l'ordonnanceur choisira un processus prêt de la classe A, pour les 3 suivantes dans la classe B, etc, et recommencera.

Ce système a l'avantage

- de respecter les priorités,

- d'interdire les coalitions.

Dans l'exploitation en traitement par lots, les classes permettaient une segmentation de la clientèle des centres de calculs : les tarifs étaient plus élevés pour les travaux dans la classe la plus prioritaires. Les clients "en classe économique" devaient attendre les résultats plus longtemps.

## **Chapitre 3**

## Gestion de la Mémoire

### 3.1 Mémoire et multi-programmation

#### 3.1.1 Motivation

Rappelons que, dès les débuts de l'informatique, il y avait une motivation d'ordre économique : tirer le meilleur profit d'un matériel qui, à l'époque, était extrêmement coûteux.

(début années 60 : le calculateur Burroughs B5000)

On s'est aperçu rapidement que le goulet d'étranglement (bootleneck) du système informatique (processeur, mémoire, périphériques)

une unité de traitement ...

n'était pas la partie la vitesse de calcul du processeur, mais la lenteur relative des périphérique : la partie la plus coûteuse (le processeur) passait son temps à attendre la fin des entrées-sorties.

des périphériques ...

D'où l'idée de partager le temps de calcul entre plusieurs programmes, ce qui permet de mieux rentabiliser les équipements (meilleurs taux d'occupation).

Nous allons voir dans ce chapitre les techniques qui ont été mises en place au cours du temps pour permettre la présence de plusieurs processus en mémoire.

L'aboutissement en est ce qu'on appelle la **mémoire virtuelle**, qui est de nos jours, en général, une combinaison de techniques de *segmentation*, de *pagination* et de va-et-vient sur disque. à la demande.

Repères historiques : le principe de la mémoire virtuelle a été exposé en 1962 dans un article de James Kilburn (Manchester) décrivant l'ordinateur Atlas. Dans les années 1970, cette technique était utilisée dans tous les ordinateurs <sup>1</sup>.

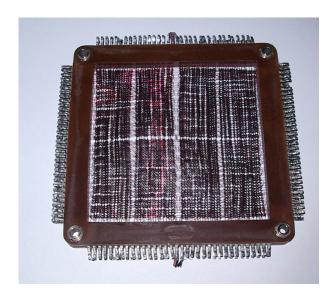

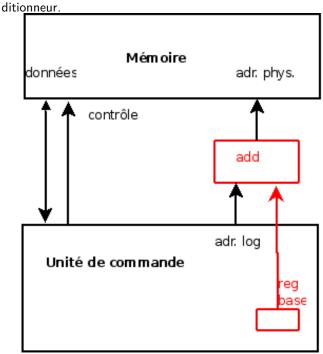

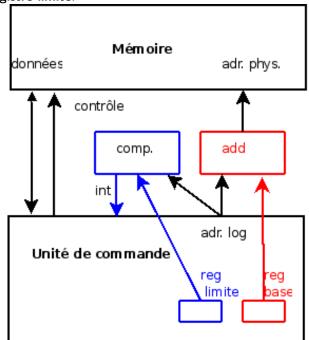

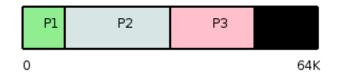

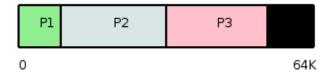

#### 3.1.2 Rappel : fonctionnement de la mémoire

Différentes technologies ont été utilisées pour réaliser les mémoires des ordinateurs : bascules bistables à base de tubes (triodes), mémoires à tores de ferrite, à transistors, circuits intégrés etc.